上篇終於講完OpenOCD基礎的架構和實用的Commands、Help APIs,

這篇開始,終於要進入RISC-V底層架構的部分啦!!!

當然還是要來講古一下啦 擴充篇幅,

官方網站: RISC-V Foundation | Instruction Set Architecture (ISA)

然後是引用Wiki的部分:

RISC-V(發音為「risk-five」)是基於已建立的精簡指令集(RISC)原則的一個開源指令集架構(ISA)。

與大多數指令集相比,RISC-V指令集可以自由地用於任何目的,允許任何人設計、製造和銷售RISC-V晶片和軟體。雖然這不是第一個開源指令集,但它具有重要意義,因為其設計使其適用於現代計算設備(如倉庫規模雲計算機、高端行動電話和微小嵌入式系統)。設計者考慮到了這些用途中的性能與功率效率。該指令集還具有眾多支持的軟體,這解決了新指令集通常的弱點。

該項目2010年始於加州大學柏克萊分校,但許多貢獻者是該大學以外的志願者和行業工作者。

RISC-V指令集的設計考慮了小型、快速、低功耗的現實世界實現,但沒有對特定微架構風格的過度架構。

截至2017年5月,用戶空間的指令集版本2.2已固定,特權指令集已處在草案版本1.10。

---引用自: RISC-V Wiki

巴拉巴拉巴拉,剩下自己看Wiki,不重要!!!

關於RISC-V中ISA的設計、功能、實作和細節等等,並不是這次鐵人賽系列文中的重點,

有興趣可以自行翻閱底下的幾份參考文件:

另外推薦我們隊長的系列文: 與妖精共舞:在 RISC-V 架構上使用 GO 語言實作 binutils 工具包

簡單的來說,原先RISC-V架構中並沒有討論到Debug Support的部分,

不過國外某家廠商(Sifive)率先提出了一套"RISC-V External Debug Support",並將其實作在該公司的IP中!

相關Spec討論可以在這邊找到: RISC-V External Debug Support 0.13

目前External Debug Spec.目前有兩套,分別是0.11和0.13版,但0.13版還在討論階段中,

所以注意: 本文所寫的內容,有可能在未來不適用,或實作細節不同,還請讀者小心服用!

本文之後討論的Spec以"Tue Nov 28 07:54:42 2017 -0800 commit: f7f3277d78d5b72dbba7d718d40892c469ca22ba"為主!

相關的警告訊息:Warning! This draft speci cation will change before being accepted as standard, soimplementations made to this draft speci cation will likely not conform to the futurestandard.

---引用自RISC-V External Debug Support 0.13

另外,如果需要最新Spec.相關討論和參與的話,可以參考這個連結:

Working Draft of the RISC-V Debug Specification Standard

如果有需要的話,也一併參考The RISC-V Instruction Set Manual Volume II:Draft Privileged ISA Specification

以下是Spec.中的目錄,也同時是未來的幾天中的主題:

經過上面拉拉拉拉講了一大堆的東西後,終於正式進入主題,

那我們就簡單的看一下整體架構的部分!!其實只是覺得天氣突然又變得太冷了,隨便打一點就想回被窩看書...

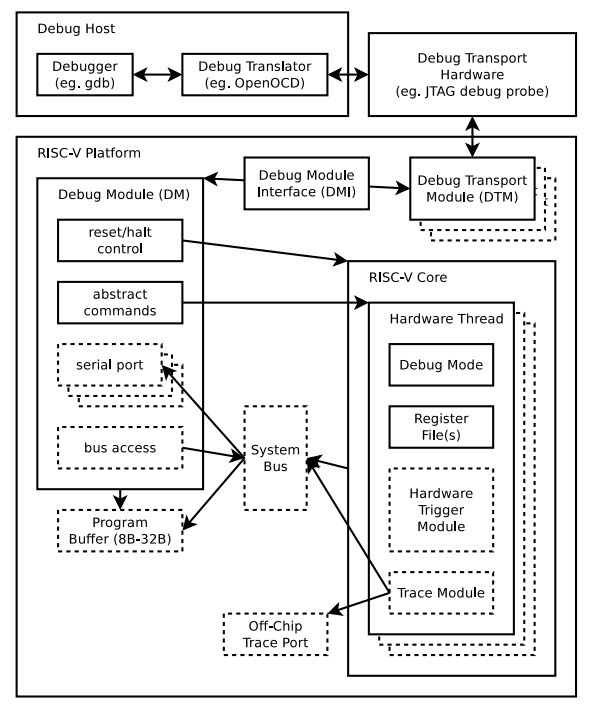

不囉嗦,先上圖~!!

---引用自RISC-V External Debug Support 0.13

首先分別介紹幾個名詞:

再來介紹一下跟Target端有關的名詞:

另外有些進階功能的地方:

以上就是Overview的部分,很淺顯XD

當作概觀來看一下,下篇開始將介紹Debug Module和其實作的內容!!